„Tiva C” változatai közötti eltérés

Nincs szerkesztési összefoglaló |

a Levédte a(z) Tiva C lapot ([Szerkesztés=Csak adminisztrátoroknak engedélyezett] (határozatlan) [Átnevezés=Csak adminisztrátoroknak engedélyezett] (határozatlan)) |

(Nincs különbség)

| |

A lap jelenlegi, 2014. május 29., 11:46-kori változata

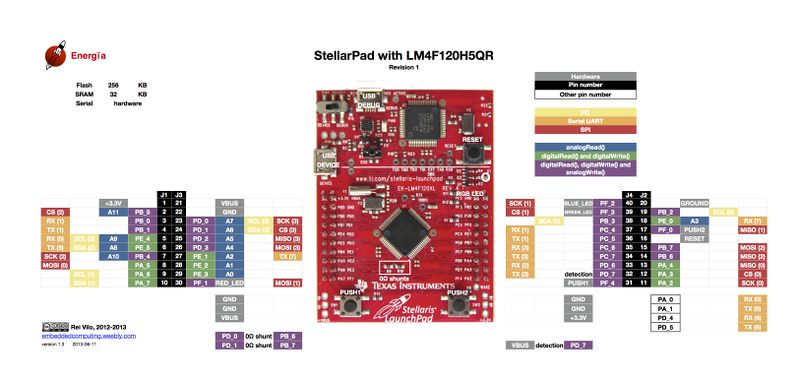

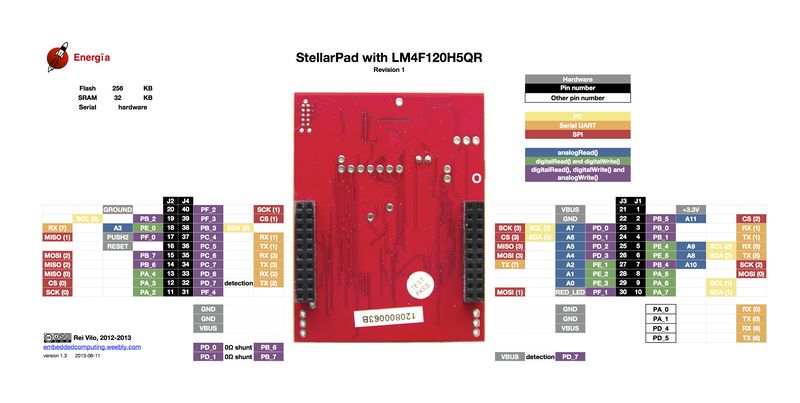

Pin map

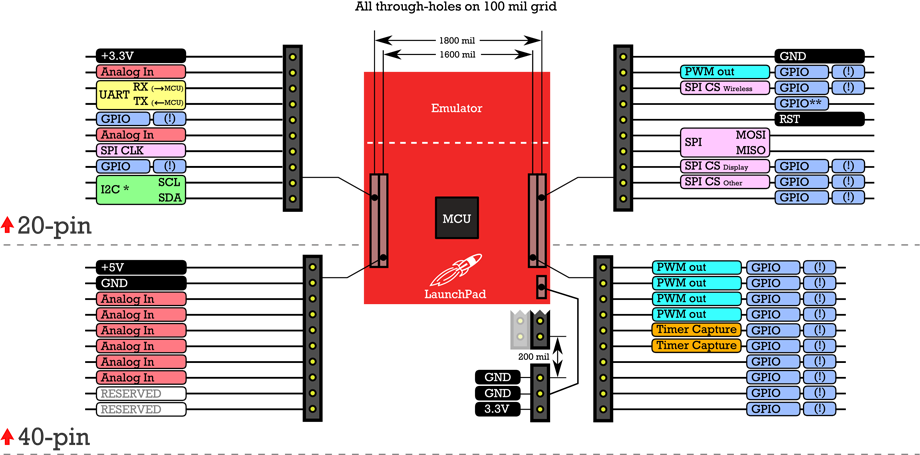

BoosterPack Pinout Standard

Pins Functions

|

IO |

Ain |

0 |

1 |

2 |

3 |

4 |

5 |

6 |

7 |

8 |

9 |

14 |

|

PA0 |

|

Port |

U0Rx |

|

|

|

|

|

|

CAN1Rx |

|

|

|

PA1 |

|

Port |

U0Tx |

|

|

|

|

|

|

CAN1Tx |

|

|

|

PA2 |

|

Port |

|

SSI0Clk |

|

|

|

|

|

|

|

|

|

PA3 |

|

Port |

|

SSI0Fss |

|

|

|

|

|

|

|

|

|

PA4 |

|

Port |

|

SSI0Rx |

|

|

|

|

|

|

|

|

|

PA5 |

|

Port |

|

SSI0Tx |

|

|

|

|

|

|

|

|

|

PA6 |

|

Port |

|

|

I2C1SCL |

|

M1PWM2 |

|

|

|

|

|

|

PA7 |

|

Port |

|

|

I2C1SDA |

|

M1PWM3 |

|

|

|

|

|

|

PB0 |

|

Port |

U1Rx |

|

|

|

|

|

T2CCP0 |

|

|

|

|

PB1 |

|

Port |

U1Tx |

|

|

|

|

|

T2CCP1 |

|

|

|

|

PB2 |

|

Port |

|

|

I2C0SCL |

|

|

|

T3CCP0 |

|

|

|

|

PB3 |

|

Port |

|

|

I2C0SDA |

|

|

|

T3CCP1 |

|

|

|

|

PB4 |

Ain10 |

Port |

|

SSI2Clk |

|

M0PWM2 |

|

|

T1CCP0 |

CAN0Rx |

|

|

|

PB5 |

Ain11 |

Port |

|

SSI2Fss |

|

M0PWM3 |

|

|

T1CCP1 |

CAN0Tx |

|

|

|

PB6 |

|

Port |

|

SSI2Rx |

|

M0PWM0 |

|

|

T0CCP0 |

|

|

|

|

PB7 |

|

Port |

|

SSI2Tx |

|

M0PWM1 |

|

|

T0CCP1 |

|

|

|

|

PC4 |

C1- |

Port |

U4Rx |

U1Rx |

|

M0PWM6 |

|

IDX1 |

WT0CCP0 |

U1RTS |

|

|

|

PC5 |

C1+ |

Port |

U4Tx |

U1Tx |

|

M0PWM7 |

|

PhA1 |

WT0CCP1 |

U1CTS |

|

|

|

PC6 |

C0+ |

Port |

U3Rx |

|

|

|

|

PhB1 |

WT1CCP0 |

USB0epen |

|

|

|

PC7 |

C0- |

Port |

U3Tx |

|

|

|

|

|

WT1CCP1 |

USB0pflt |

|

|

|

PD0 |

Ain7 |

Port |

SSI3Clk |

SSI1Clk |

I2C3SCL |

M0PWM6 |

M1PWM0 |

|

WT2CCP0 |

|

|

|

|

PD1 |

Ain6 |

Port |

SSI3Fss |

SSI1Fss |

I2C3SDA |

M0PWM7 |

M1PWM1 |

|

WT2CCP1 |

|

|

|

|

PD2 |

Ain5 |

Port |

SSI3Rx |

SSI1Rx |

|

M0Fault0 |

|

|

WT3CCP0 |

USB0epen |

|

|

|

PD3 |

Ain4 |

Port |

SSI3Tx |

SSI1Tx |

|

|

|

IDX0 |

WT3CCP1 |

USB0pflt |

|

|

|

PD4 |

USB0DM |

Port |

U6Rx |

|

|

|

|

|

WT4CCP0 |

|

|

|

|

PD5 |

USB0DP |

Port |

U6Tx |

|

|

|

|

|

WT4CCP1 |

|

|

|

|

PD6 |

|

Port |

U2Rx |

|

|

M0Fault0 |

|

PhA0 |

WT5CCP0 |

|

|

|

|

PD7 |

|

Port |

U2Tx |

|

|

|

|

PhB0 |

WT5CCP1 |

NMI |

|

|

|

PE0 |

Ain3 |

Port |

U7Rx |

|

|

|

|

|

|

|

|

|

|

PE1 |

Ain2 |

Port |

U7Tx |

|

|

|

|

|

|

|

|

|

|

PE2 |

Ain1 |

Port |

|

|

|

|

|

|

|

|

|

|

|

PE3 |

Ain0 |

Port |

|

|

|

|

|

|

|

|

|

|

|

PE4 |

Ain9 |

Port |

U5Rx |

|

I2C2SCL |

M0PWM4 |

M1PWM2 |

|

|

CAN0Rx |

|

|

|

PE5 |

Ain8 |

Port |

U5Tx |

|

I2C2SDA |

M0PWM5 |

M1PWM3 |

|

|

CAN0Tx |

|

|

|

PF0 |

|

Port |

U1RTS |

SSI1Rx |

CAN0Rx |

|

M1PWM4 |

PhA0 |

T0CCP0 |

NMI |

C0o |

|

|

PF1 |

|

Port |

U1CTS |

SSI1Tx |

|

|

M1PWM5 |

PhB0 |

T0CCP1 |

|

C1o |

TRD1 |

|

PF2 |

|

Port |

|

SSI1Clk |

|

M0Fault0 |

M1PWM6 |

|

T1CCP0 |

|

|

TRD0 |

|

PF3 |

|

Port |

|

SSI1Fss |

CAN0Tx |

|

M1PWM7 |

|

T1CCP1 |

|

|

TRCLK |

|

PF4 |

|

Port |

|

|

|

|

M1Fault0 |

IDX0 |

T2CCP0 |

USB0epen |

|

|